咨询热线:

17715390137

18101240246

18914047343

邮件:mxenes@163.com

扫码关注或微信搜索公众号:

二维材料Fronrier

关注后点击右下角联系我们,

进入企业微信。

专业服务在线

腾龙国际上下分客服【521006914微信QQ同步】腾龙官方网站(www.TL9043.com)腾龙国际客服24小时在线,【公司直属客服】【公司直属开户】【大额无忧】支持视频验证现场。

研究背景

二维(2D)半导体作为晶体管的超薄沟道材料已经引起了广泛的关注。原子薄特性和无悬挂键的自由表面为晶体管缩放提供了巨大的潜力,这对于减少断态功耗和进一步扩展摩尔定律至关重要。迄今为止,2D晶体管的主要挑战是不可控的器件极性(n型或p型)和多数载流子类型,这对在2D晶体管中实现互补CMOS逻辑功能构成了关键限制。在现代硅微电子学中,硅沟道的掺杂浓度和晶体管极性是通过高能离子注入和随后的高温活化引入非本征掺杂原子来实现的。然而,将这种方法应用于2D半导体并不容易,因为在这种原子薄的晶格中,杂质掺杂的物理空间很小。因此,2D晶体管的多数载流子类型受到其固有特性的限制。

在过去的几年中,为实现2D CMOS功能付出了巨大的努力。早期的尝试着重于使用两种不同的2D半导体,其中一种材料用于NMOS(例如MoS2和MoSe2),另一种材料用于PMOS(例如黑磷和WSe2)。尽管能够演示所需的逻辑功能,但该方法仍依赖于不可控的本征掺杂,并且与CMOS工艺不兼容。还可以通过在2D半导体和被吸附物之间进行电荷转移过程,通过化学表面吸附来实现2D半导体的选择性掺杂,这可以有效地调节2D载流子浓度及多数载流子类型(电子或空穴)。然而,由于表面掺杂和2D材料之间的弱相互作用,这种化学吸附方法通常稳定性较差。最近,还使用具有不同功函数的金属在2D沟道中演示了CMOS逻辑功能。但是,由于强大的费米能级钉扎效应,无论使用何种金属功函数,通常都在2D/金属界面中都观察到较大的肖特基势垒。

成果介绍

有鉴于此,近日,湖南大学刘渊教授、美国加州大学洛杉矶分校段镶锋教授以及西北工业大学冯丽萍教授(共同通讯作者)合作报道了一种无掺杂策略,使用相同的接触金属但采用不同的集成方法来调制WSe2晶体管的极性。通过对Au电极进行低能范德华集成,观察到了稳定且优化的p型晶体管性能,这与在同一WSe2薄片上使用具有明显n型特性的常规沉积的Au接触制备的晶体管形成了鲜明的对比。通过切换多数载流子类型并实现电子和空穴的最佳接触,展示了一种无掺杂逻辑反相器,在5.5 V的偏置电压下具有340的高电压增益。此外,本文还扩展了简单的极性控制方法,实现了更复杂的逻辑功能,例如NAND和NOR。文章以“Doping-free complementary WSe2 circuit via van der Waals metal integration”为题发表在著名期刊Nature Communications上。

图文导读

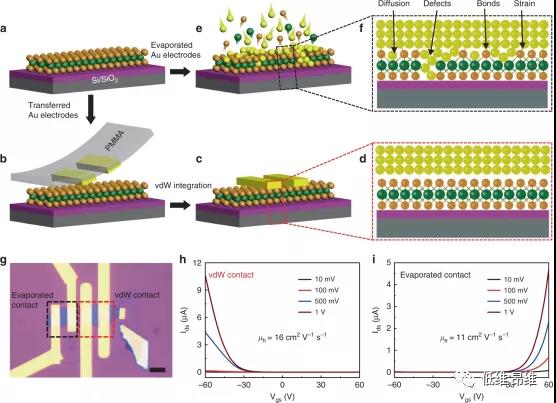

图1. 器件结构的示意图和电学测试。(a-c)使用vdW集成工艺制备WSe2晶体管的过程:将WSe2薄片剥离到Si/SiO2衬底上;预制的Au电极以弱vdW相互作用物理层压在WSe2表面上。(d)与WSe2 vdW接触的截面示意图,表明界面清洁且尖锐。(e)使用常规热蒸发在WSe2上蒸发Au电极。(f)与WSe2蒸发接触的截面示意图,表明界面高度无序。(g)器件的光学图像。(h&i)使用vdW集成和常规蒸发电极的WSe2晶体管的Ids-Vgs转移特性。通过控制金属集成方法,器件极性可以在p型和n型之间切换,载流子迁移率分别为16和11 cm2V-1s-1(偏置为1 V)。

图1a-f示意性地给出了器件结构。为了制备该器件,首先将具有各种厚度的多层WSe2薄片机械剥离到具有300 nm氧化硅(作为栅极电介质)的重掺杂硅衬底(作为栅极)上。接下来,在Si晶圆上预制50 nm Au电极对,然后使用先前开发的方法机械释放。释放的金属电极在显微镜下对准,并使用vdW金属集成工艺物理层压在WSe2薄片的顶部,从而产生原子级尖锐且干净的Au/WSe2界面(图1a-d)。为了进行比较,还使用常规的电子束光刻技术在同一WSe2薄片上沉积了另一对具有相同厚度(50 nm)的金电极,然后进行高真空热沉积,会导致具有扩散、缺陷、化学键和应变的非理想金属/半导体界面,如图1e和f。器件的光学图像如图1g所示,其中左电极对是通过热蒸发制备的,而右电极对是vdW集成的。室温下,在真空中进行了器件的电学输运研究。如图1h所示,与vdW金属电极接触的器件(约7 nm)表现出p型Ids-Vgs转移特性,与WSe2和高功函数Au的能带排列一致,表明使用vdW金属集成方法可以优化Au/WSe2界面。相反,在不进行任何掺杂工艺的情况下,在使用常规沉积的Au接触的器件中观察到n型Ids-Vgs转移特性(图1i)。观察到的极性变化表明在蒸发的Au/WSe2界面内费米能级钉扎效应很强,其中钉扎的费米能级位置靠近WSe2的导带。从该器件中提取的空穴和电子迁移率分别为16和11 cm2V-1s-1。

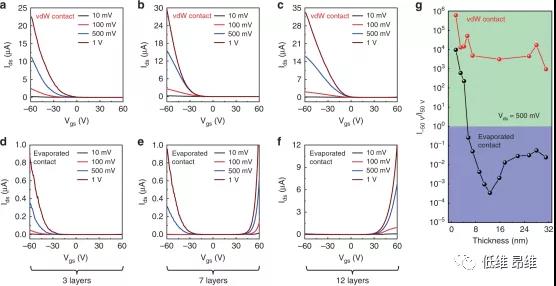

图2. 带vdW集成和蒸发Au电极的WSe2晶体管的厚度依赖性电学测量。(a-c)使用vdW Au电极,不同厚度(3L,7L和12L)WSe2的Ids-Vgs转移曲线,其中始终观察到p型行为。(d-f)使用常规沉积的Au电极,不同厚度(3L,7L和12L)WSe2的Ids-Vgs转移曲线,分别观察到p型,双极性和n型行为。(g)I-50V和I50V之间的电流比作为WSe2厚度的函数。对于带有vdW电极的器件,观察到较大的I-50V/I50V比>103,这表明与沟道厚度无关,p型行为始终如一。对于具有常规沉积的Au电极的器件,随着厚度的增加,I-50V/I50V会降低,其中可以清楚地看到从p型到n型的转变。

为了进一步确认这种电学行为的稳定性并通过使用不同的金属集成工艺来研究极性控制,对各种厚度的WSe2进行了详细的电学测量。如图2a-c所示,无论WSe2的厚度如何,与vdW金属电极接触的器件都表现出明显的p型行为,与WSe2价带(从单层到块材5.02-4.83 eV)和高功函数Au(5.24 eV)之间的能带排列一致。与之形成鲜明对比的是,对比器件(与常规蒸发的Au电极接触)随着WSe2厚度的增加表现出独特的极性变化行为,展示了厚度小于5层(~3 nm)的p型特性,厚度为7层(~4.5 nm)的双极性特性以及厚度大于10层(~6.5 nm)的n型特性,如图2d-f所示。

此外,为确认该行为的稳定性并定量分析极性变化,测量了20多个器件,并提取了I-50V(Vg=-50 V时的Ids)和I50V(Vg=50 V时的Ids)之间的电流比作为WSe2厚度的函数。I-50V/I50V之比在这里可以表示给定晶体管中空穴与电子贡献之间的比率,因此可以定量地证明晶体管的极性和多数载流子类型。对于带有vdW接触电极的器件,当WSe2从单层到30 nm(约50层)厚,始终观察到超过103的I-50V/I50V比,表明无论厚度如何,p型行为始终占主导地位(电子电流可以忽略不计)。相比之下,对于具有常规蒸发电极接触的器件,随着厚度从单层增加到~50层,I-50V/I50V比从104下降到~10-3(7个数量级),这表明多数载流子类型可以通过增加WSe2的厚度从空穴逐渐转变为电子。蒸发接触(厚度>13 nm)的I-50V/I50VV比略有增加,可以归因于垂直电阻(在接触区域下方)随厚度增加而增加。

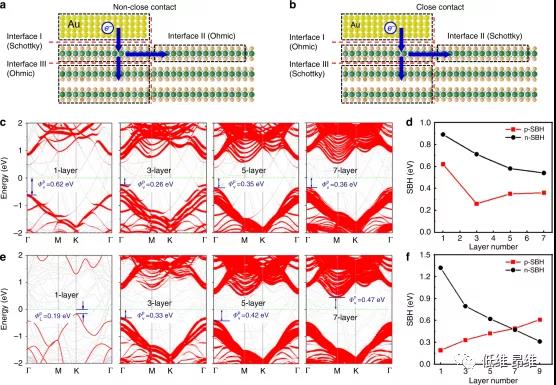

图3. 具有不同接触方式的Au/WSe2界面的DFT计算。(a&b)Au/WSe2非紧密接触模型和紧密接触模型的截面示意图。(c)对于非紧密接触模型,计算了不同厚度(在Au接触下)WSe2的能带结构。(d)对于非紧密接触模型,计算出SBH随WSe2层数的变化,在该模型中始终观察到p型SBH占主导地位。(e)对于紧密接触模型,计算了不同厚度(在Au接触下)WSe2的能带结构。(f)对于紧密接触模型,计算出SBH随WSe2层数的变化,随着层厚的增加从p型SBH明显过渡到n型SBH。

为了进一步了解使用不同金属集成方法进行极性控制的机制,并深入研究从PMOS到NMOS转变的厚度依赖性,对金属/WSe2界面上的载流子输运进行了DFT模拟。首先,构造了两种类型的Au/WSe2界面模型:对应于蒸发Au界面的紧密接触模型和对应于vdW集成Au界面的非紧密接触模型。对于紧密接触模型,在金属和WSe2之间选择了1.5 Å的层间距离(Au和Se的共价半径),在该距离下,Au和Se原子共价键合。对于非紧密接触模型,使用的层间距离为3.3 Å,其中在紧密接触层间距离的基础上增加了1.8 Å的vdW间隙距离。基于此模型,存在三个可能导致输运势垒的界面:Au和第一层WSe2(界面I),接触下方和沟道区域内部(界面II)的WSe2以及第一层WSe2和其余的WSe2层(界面III),如图3a和b所示。

对于非紧密接触,由于Au/WSe2的层间距离足够大且它们的层间相互作用较弱,因此Au电极对WSe2的性能影响很小。WSe2中的界面间隙状态可以忽略不计,并且整个多层WSe2保持其表征特性,从而导致在界面II和III处发生欧姆接触。因此,无论WSe2的厚度如何,接触肖特基势垒仅存在于界面I中。图3c给出了vdW Au接触下WSe2的计算能带结构,进一步表明了Au电极与下面WSe2之间的弱相互作用。SBH的计算结果如图3d所示,其中以p型肖特基势垒为主,与使用vdW Au接触观察到的p型晶体管行为一致(图2a-c)。

与之形成鲜明对比的是,对于紧密接触模型,Au电极与WSe2之间存在化学相互作用,从而强烈干扰WSe2的电学性能。在WSe2的禁带中会生成大量的界面态,导致WSe2带隙消失。因此,如图3b所示,第一层WSe2在接触下方被金属化(具有新的功函数~4.83 eV),从而在界面I处形成欧姆接触。同时,在电荷从金属化WSe2输运到半导体WSe2的过程中,在界面II和III处产生了肖特基势垒。对于单层WSe2,界面II处的横向肖特基势垒为p型,势垒高度为0.19 eV。而另一方面,对于多层WSe2,第一层WSe2被金属化,但是其余的层在很大程度上保持本征,因此界面III处的肖特基势垒的影响越来越明显。如图3e和f所示,当Au电极与3层和5层WSe2接触时,计算出界面III处的垂直肖特基势垒为p型,并逐渐转变为7层和9层WSe2时的n型,与在图2d-g中的测量结果一致。图3f展示了界面III处SBH随层数的变化。

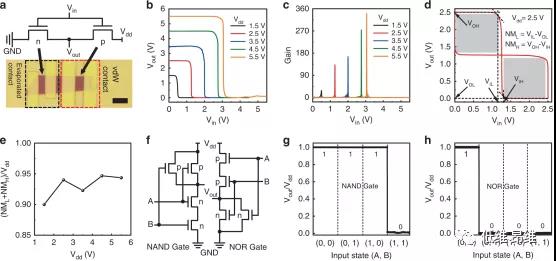

图4. 基于不同接触方式的WSe2晶体管的CMOS逻辑功能。(a)典型的互补反相器的电路图和光学图像,由两个串联的WSe2晶体管组成,其中一个与沉积的Au电极(n型)接触,另一个与vdW Au电极(p型)接触。(b)反相器的电压传输特性随输入电压的变化。(c)所得反相器的相应电压增益。(d)WSe2 CMOS逻辑反相器的双稳态滞后电压传输特性随输入电压(Vdd=2.5 V)的变化,实现了1.16 V的低噪声容限(NML)和1.19 V的高噪声容限(NMH)。(e)总噪声容限与Vdd的函数关系。(f)由四个WSe2晶体管组成的NAND和NOR电路图,其中两个与沉积的Au电极接触作为n型器件,另外两个与vdW电极接触(p型)。(g&h)NAND和NOR电路的输入-输出逻辑功能。

通过控制晶体管的极性,可以很容易地将多个WSe2晶体管集成到功能电路中。 例如,可以通过串联连接两个WSe2晶体管来实现互补逻辑反相器,其中一个器件与沉积的Au电极接触作为n型器件,另一器件与vdW Au电极接触作为p型器件。反相器的逻辑图和光学图像如图4a所示,除了将背栅电介质从300 nm厚的SiO2更改为20 nm厚的Al2O3以增强栅极电容和对沟道的静电控制,这对于降低反相器输入电压和增加电压增益至关重要。

图4b显示了所得反相器的电压传输特性与输入电压的关系,偏置电压(Vdd)为1.5至5.5 V,演示了随输入电压的急剧变化。在图4c中绘制了所得的电压增益,在Vdd=5.5 V时峰值为340,是基于TMD的反相器的最高值。进一步增加Vdd会导致栅极漏电流大大增加,并降低整体器件性能。此处获得的更高电压增益可以很大程度上归因于通过控制它们的费米能级位置来优化PMOS和NMOS的接触,这与蒸发具有不同功函数金属的方法相比本质上是不同的,在先前方法中,由于金属/2D界面上的费米能级钉扎效应强,因此难以实现与PMOS和NMOS的最佳接触。为了表征通过不同接触方法制备的反相器的稳定性,提取了噪声容限(NML和NMH),如图4d所示。在Vdd为2.5 V时,实现了1.16 V的NML和1.19 V的NMH。此外,还绘制了总噪声容限与Vdd的关系(图4e),在各种偏置电压下,反相器测得的总噪声容限大于90%,表明对噪声的耐受性很高。

更进一步,通过将更多的WSe2晶体管连接在一起,可以实现更复杂的逻辑功能。例如,可以使用四个多层WSe2晶体管构建逻辑NOR或NAND功能,如图4f的电路图所示。所测得的输入和输出电压清楚地证明了NOR和NAND所需的逻辑功能(图4g和h),展示出将其用于更复杂电路的潜力。

总结与展望

本文展示了使用相同的接触金属Au和相同的沟道材料WSe2,但是使用不同的金属集成方法来控制2D晶体管极性的无掺杂策略。通过详细的厚度依赖性测量和DFT计算,发现独特的极性变化可能归因于使用不同金属集成方法的可控费米能级钉扎(或去钉扎)效应。此外,通过与PMOS和NMOS的优化接触,展示了逻辑反相器,其最高电压增益为340(在Vdd为5.5 V时),总噪声容限超过90%,并且具有更复杂的CMOS功能,例如NAND和NOR。本文的研究结果不仅演示了高性能CMOS逻辑电路,而且还提供了一种使用相同的接触金属来控制2D半导体极性的方法,从而为高性能2D电子器件和CMOS设计提供了思路。

文献信息

Doping-free complementary WSe2 circuit via van der Waals metal integration

(Nat. Commun., 2020, DOI: 10.1038/s41467-020-15776-x)

文献链接:https://www.nature.com/articles/s41467-020-15776-x

信息来源:低维 昂维

本信息源自互联网仅供学术交流 如有侵权请联系我们立即删除

|

版权所有 © 2019 北京北科新材科技有限公司

All rights reserved. 京ICP备16054715号-2 |