已传文件:photo/1631586161.png

高密度聚合物/陶瓷复合材料需要高介电响应和电绝缘,在带半导体的聚合物复合材料中,介电响应较低。为了平衡高介电常数和击穿强度,文章研究制备了具有重新合成的V2C MXene-Cuo杂化粒子的聚合物基复合材料,研究发现,复合材料的高介电响应归因于陶瓷/陶瓷异质结处的强电子极化,高绝缘性是由于氟诱导的电子阱效应。第一原理计算验证了V2C/CuO范德瓦尔斯异质结处的电子转移机理,与聚合物/CuO二元复合材料相比,聚合物/V2C-CuO三元复合材料的综合电性能(显著改善介电响应和轻微的绝缘损伤)。含10wt%V2C-CuO的三元复合材料的高介电常数为89,低介电损耗为0.23,100Hz下的低电导率为6.8×10−7Sm−1,高击穿强度为204MVm−1。文章研究使易于制备尖端纳米复合电介质成为可能。

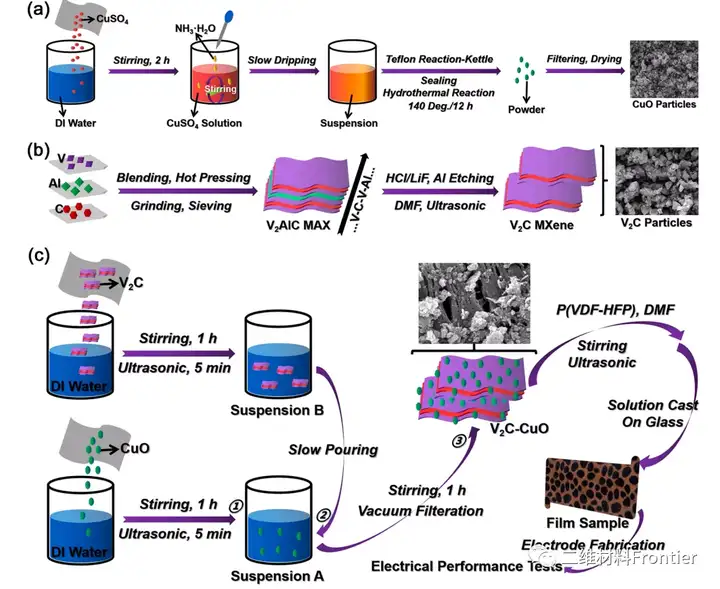

图1.(a)氧化铜、(b)V2C和(c)混合陶瓷和复合材料的方案制备步骤。

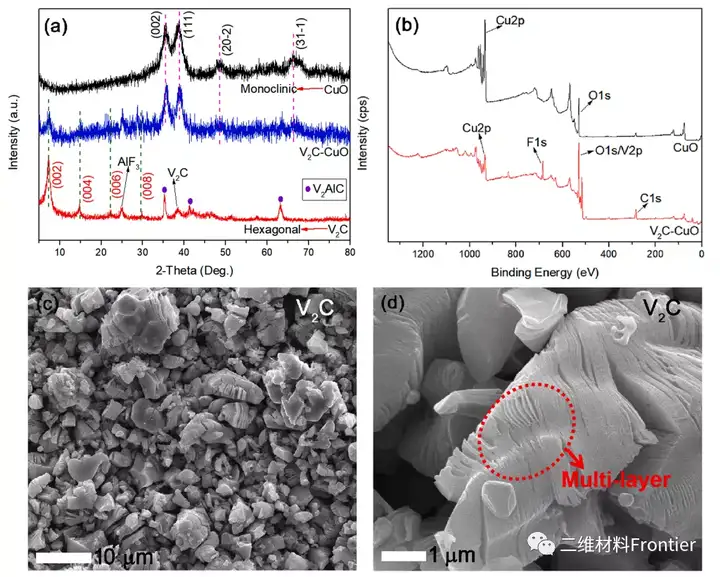

图2.(a)V2C、氧化铜和混合陶瓷的XRD,(b)XPS的氧化铜和混合陶瓷,(c)V2C的低倍扫描电镜和(d)V2C的高倍扫描电镜。

氧化铜和混合陶瓷的XPS全光谱显示,在氧化铜中,933eV和529eV的信号被分配到Cu2p和o1s上。在混合陶瓷中,检测到Cu2p和O1s信号,表明混合陶瓷中存在氧化铜。5295eV和289eV的信号来自混合陶瓷中V2C的V2p和C1。

图3.(a)氧化铜的低倍扫描电镜,(b)氧化铜的放大扫描电镜,(c)混合陶瓷的低倍扫描电镜,(d)混合陶瓷的高倍扫描电镜。

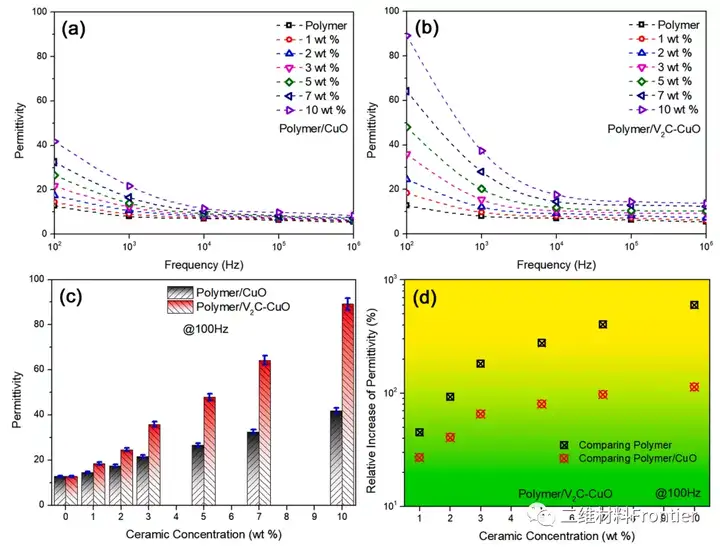

图4.(a)二元体系介电常数频谱,(b)三元体系介电常数频谱,(c)100Hz三元体系100Hz的介电常数与陶瓷含量的关系,(d)三元体系与聚合物和二元体系相比,100Hz的介电常数相对增加。

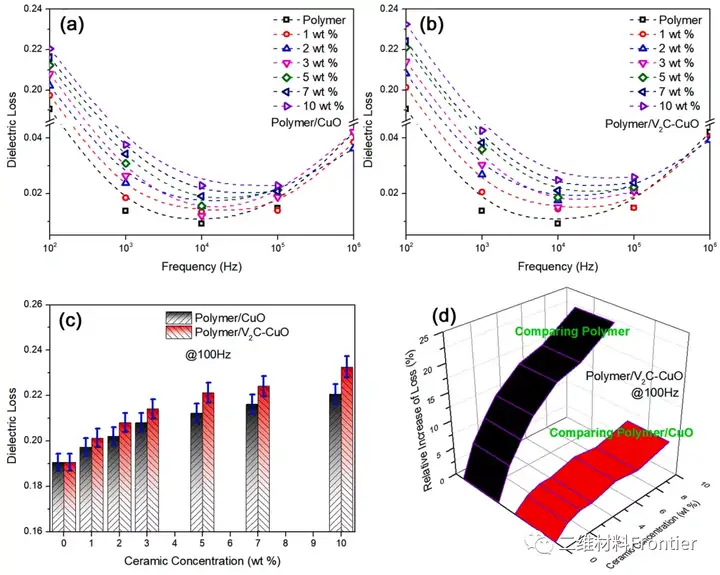

图5.(a)二元体系介电损耗频谱,(b)三元体系介质损耗频谱,(c)100Hz时双体系介电损耗与陶瓷含量的关系,(d)三元体系与聚合物和二元体系相比,100Hz时的损耗相对增加。

用V2C和氧化铜颗粒制备合成的V2C-Cuo杂化颗粒。与氧化铜相比表现出较高的高介电响应并诱导界面极化增强,大大提高了三元体系的介电常数。制备的聚合物基三元复合薄膜作为电介质。与聚合物/CuO二元体系相比,三元系统表现出提高介电常数,略微增加介电损耗和电导率,以及略微降低击穿强度。最后文章提出了基于陶瓷/陶瓷范德瓦尔斯异质结的界面铜和F的强电子极化研究三元体系的高介电响应。综上所述,三元体系的高介电常数应源于聚合物/V2C界面极化、V2C/CuO界面处的电子极化和氧化铜内的电子-空穴偶极子。高击穿性能应基于低陶瓷/陶瓷(聚合物/V2C)界面泄漏导电和均匀的现场分布。10wt%的三元复合陶瓷具有高介电常数~89,低介电损耗~0.23,100Hz低导电率~6.8×10−7sm−1,高击穿强度~204mvm−1。揭示了V2C与氧化铜之间具有较强的协同作用。

https://doi.org/10.1016/j.apsusc.2021.149008

本信息源自互联网仅供学术交流 ,如有侵权请联系我们立即删除。